[Computer Architecture] CPU 심화

3줄 요약

CPU의 성능은 클럭 속도뿐 아니라 코어, 스레드 등 구조적 요소에 따라 결정

명령어 파이프라인과 OOOE를 통해 병렬 처리 성능 향상

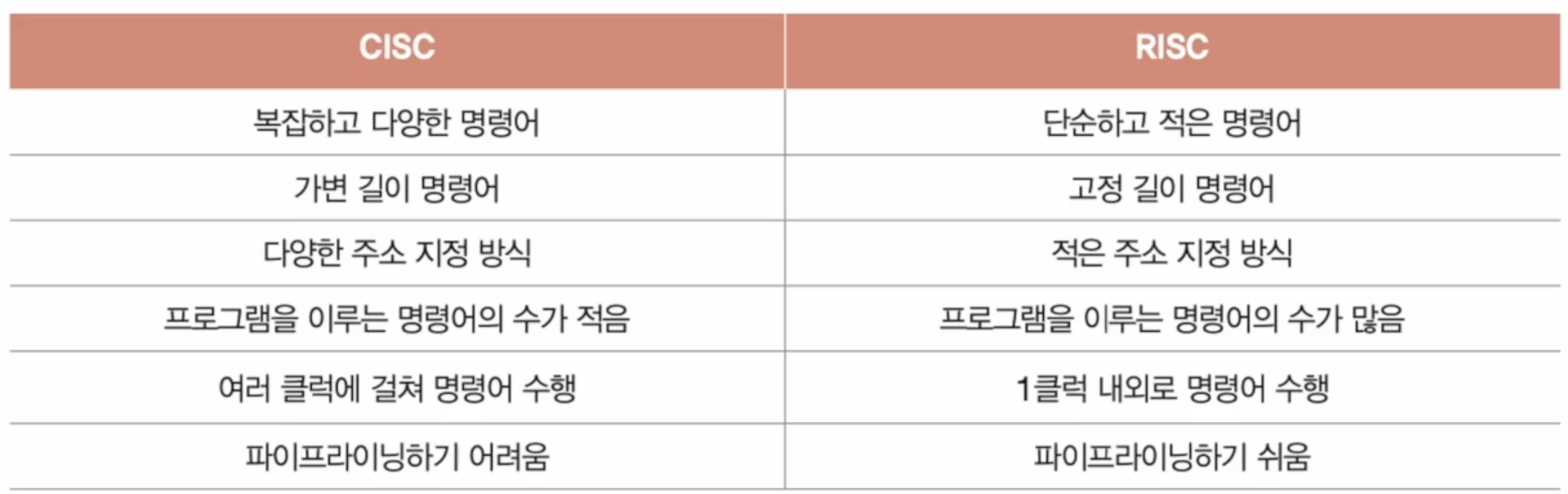

RISC와 CISC는 명령어 집합 구조의 두 가지 대표 방식

💻 컴퓨터 구조 & 운영체제 시리즈

이 시리즈는 『혼자 공부하는 컴퓨터 구조+운영체제』 (강민철 저)

+ 인프런 강의를 기반으로 개인적으로 복습 및 정리한 기록입니다.

🚀 CPU 심화

🔸 클럭 속도

- 클럭 신호에 맞춰 명령어 실행

- Hz(헤르츠) 단위 → 1초에 몇 번 클럭이 반복되는지

- 클럭 속도 증가 시 성능 향상

- 필요 이상으로 높일 시 발열, 전력 소모 증가로 이어짐

클럭 외 성능 향상 방법

- 코어 수 증가

- 스레드 수 증가

🔸 코어 (Core)

- 명령어를 실행하는 CPU 내부의 단위

- 멀티코어 → 여러 개의 코어로 병렬 처리 가능

- 코어 수 증가 ≠ 무조건 속도 증가

🔸 스레드 (Thread)

- 프로세스가 할당받은 자원을 바탕으로 실제 작업을 수행하는 실행 흐름의 단위

하드웨어적 스레드

- 하나의 코어가 동시에 처리하는 명령어 단위

- 논리 프로세서

- 레지스터가 핵심 역할

소프트웨어적 스레드

- 하나의 프로그램에서 독립적으로 실행되는 흐름 단위

🔸 명령어 병렬 처리

명령어 파이프라인

- 서로 겹치지 않는 단계는 동시에 실행 가능

- 명령어 인출 (Instruction Fetch)

- 명령어 해석 (Instruction Decode)

- 명령어 실행 (Execute Instruction)

- 결과 저장 (Write Back)

- 슈퍼스칼라 구조

- 파이프라인을 여러 개 사용하는 구조

- 병렬 처리 가능성 ↑

- 파이프라인 위험 발생 가능성 ↑

명령어 파이프라인 위험 (Hazard)

- 명령어 파이프라인이 성능 향상에 실패하는 경우(동시에 처리할 수 없는 경우)

- 명령어 병렬 처리 실패 원인

| 위험 종류 | 설명 |

|---|---|

| 데이터 위험 | 명령어 간의 데이터 의존성 |

| 제어 위험 | 프로그램 카운터의 급작스러운 변화 |

| 구조적 위험 | 여러 명령어가 동일한 하드웨어 자원을 사용할 경우 |

비순차적 명령어 처리 (OOOE, Out-of-Order Execution)

- 합법적인 새치기

- 순서를 바꾸어도 결과에 영향 없는 명령어를 먼저 실행

- 전체 실행 흐름은 그대로 유지

🔸 명령어 집합 구조 (ISA, Instruction Set Architecture)

- CPU가 이해하는 언어

- 소프트웨어가 하드웨어를 제어하기 위한 약속

🏛️ CISC (Complex Instruction Set Computer)

- 복잡하고 다양한 명령어 제공

- 가변 길이 명령어

- 소수의 명령어로 많은 기능 구현 가능

- 초기 메모리 제한 환경에 유리

- 명령어 파이프라인에 불리 (복잡한 구조로 인한 한계)

- 사용 빈도 낮은 명령어 많음

최근 CISC 구조도 파이프라이닝을 위해 내부적으로 명령어를 세분화

→ 마이크로 명령어 사용 → RISC처럼 동작

⚡ RISC (Reduced Instruction Set Computer)

- 짧고 규격화된 명령어

- 명령어 수 적음

- 메모리 접근 최소화 → load, store만 사용

- 레지스터 기반 처리

- 파이프라이닝에 유리

출처: 『혼자 공부하는 컴퓨터 구조+운영체제』 - 강민철 저

출처: 『혼자 공부하는 컴퓨터 구조+운영체제』 - 강민철 저

✅ 마무리 정리

CPU의 성능은 단순히 클럭 속도뿐만 아니라

코어, 스레드, 파이프라인, 명령어 구조 등 여러 요소에 따라 결정됩니다.

구조를 잘 이해하면, 시스템 최적화나 성능 분석 시 큰 도움이 됩니다.

📚 참고 자료

- 『혼자 공부하는 컴퓨터 구조+운영체제』 - 강민철 저

- 인프런 강의 - 혼자 공부하는 컴퓨터 구조+운영체제 기반 강의

읽어주셔서 감사합니다 🙌

내용이 도움이 되었거나, 틀린 부분이 있다면 댓글이나 GitHub Issue로 알려주세요 😊

This post is licensed under CC BY 4.0 by the author.